盖世汽车讯 据外媒报道,东京工业大学(Tokyo Institute of Technology)的科学家报告称,两种创新设计技术可显著提高分数N锁相环(PLL)的性能。

所提出的方法旨在最大限度地减少称为分数杂散的不需要的信号,这种信号通常困扰许多现代雷达系统和无线收发器中使用的PLL。这些努力可以为5G时代之后无线通信、自动驾驶汽车、监控和跟踪系统的技术改进打开大门。

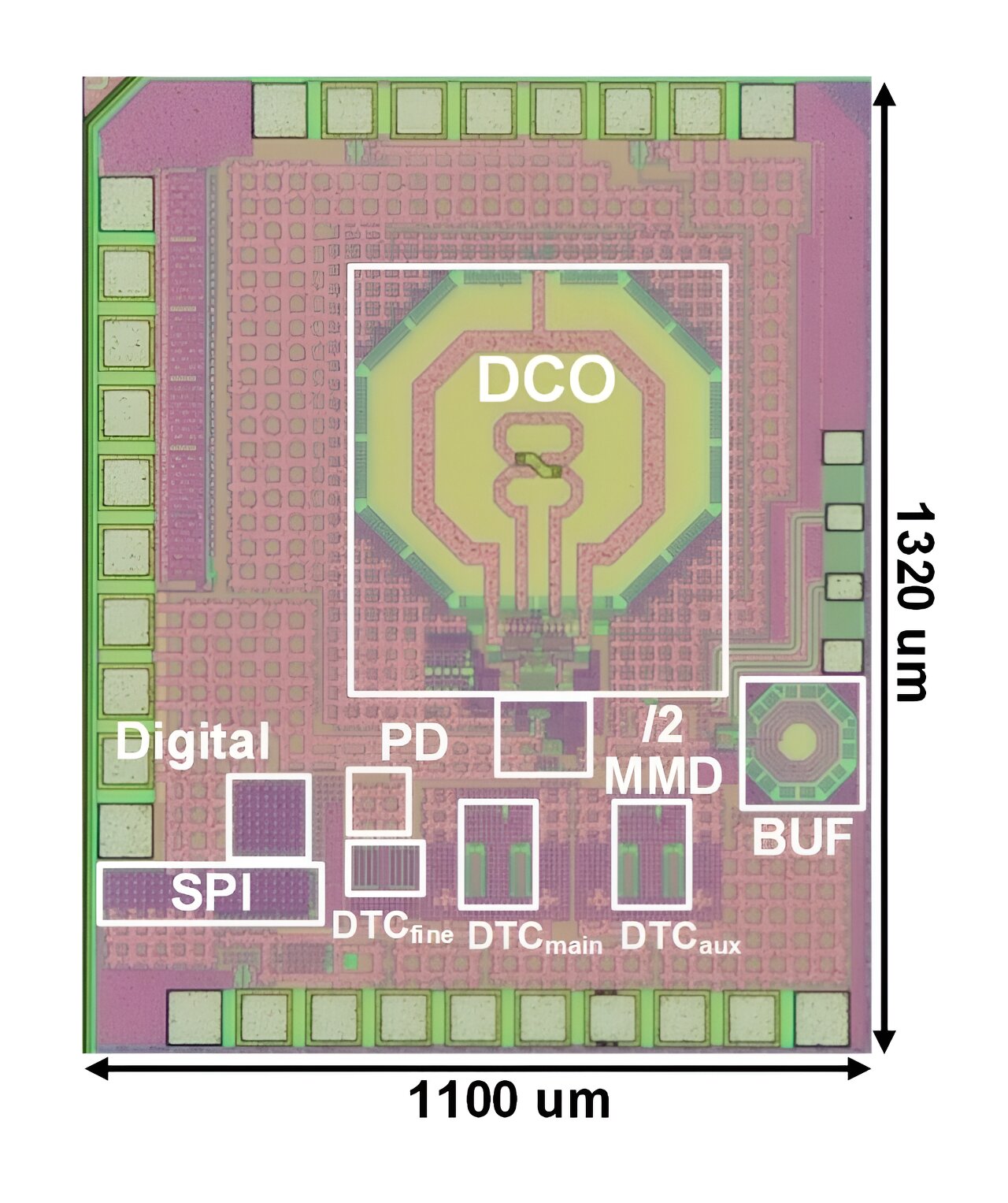

许多新兴和不断发展的技术,例如自动驾驶车辆、目标跟踪系统和远程传感器,都依赖于无线数据收发器和雷达系统的高速、无差错运行。在这些应用中,锁相环(PLL)是帮助振荡信号合成、调制和同步的关键组件。因此,消除或最小化PLL中的误差源对于提高系统的整体性能至关重要。

在分数N PLL中,一种流行的PLL类型具有出色的分辨率和对频率、抖动和分数杂散的灵活控制,其中“抖动”是指与合成振荡的理想时序的总体偏差。另一方面,分数杂散是由于误差的周期性而产生的不需要的信号。

*特别声明:本文为技术类文章,禁止转载或大篇幅摘录!违规转载,法律必究。

本文地址:https://auto.gasgoo.com/news/202402/20I70382940C409.shtml

好文章,需要你的鼓励

联系邮箱:info@gasgoo.com

求职应聘:021-39197800-8035

简历投递:zhaopin@gasgoo.com

客服微信:gasgoo12 (豆豆)

新闻热线:021-39586122

商务合作:021-39586681

市场合作:021-39197800-8032

研究院项目咨询:021-39197921