全球性芯片短缺已持续两年,深层原因在于:智能电动汽车市场的增量态势,与黑天鹅频发阻碍生产与运输形成供需矛盾,由于新产业链形成需要一定周期,缺芯潮似乎没有在短期内解决的可能性。

与此同时,汽车电子电气架构正走向中央计算时代,芯片算力飞速迭代,既带来了行业机遇,也是悬在供应企业头顶的达摩克里斯之剑:

如何在软件智能化程度及部署复杂度不断拔高的同时保障产品可靠性?如何在代码数成倍增长的同时加快供应速度?如何在芯片飞速迭代的情况下提高良率与安全性?

作为众多科技公司的Silicon to Software™(“芯片到软件”)合作伙伴,新思科技与诸多顶尖芯片提供商有紧密合作。针对“加速SoC设计成型,助推国产芯片上车”的行业痛点,新思科技提出了IP车规级, EDA全流程芯片设计解决方案、软硬件协同虚拟原型技术、芯片生命周期管理(SLM)等解决方案。

图片来源:新思科技 官网

IP先行,助力消费级芯片提升至车规级

伴随汽车电子电气架构从分布式E/E架构转向功能域,原本分散的ECU被集成为网关、座舱智能、自动驾驶几大功能域,这一趋势带来了算力集中化的潮流,由此,智能车所使用半导体的数量和价值都在呈倍数增长。

芯片及其相关产业正从消费级向车规级领域扩张,而要从消费级转向车规级,成熟的IP方案必不可少:如果将芯片制造比作搭建房屋,那么半导体IP就是标准规格图纸,一份准确合规的图纸可以大幅降低芯片设计制造过程中的不确定性。

新思科技汽车业务拓展总监武钰表示,与消费级产品相比,车规级产品有更长的寿命要求:一般是15~20年,而PPM曲线(失效率,在一百万个零部件中故障部件的占比)平均低于1,甚至近趋于零。

图片来源:新思科技

为兼顾更长的使用期限和更高的良率,车规级芯片在进行半年到一年的产线认定之后,原则上不可以更改生产设备和制程步骤与时间。因此,在芯片制造设计环节就确保其可靠性,助推其通过行业标准验证,是降本增效的关键路径。

据武钰介绍, 新思科技IP套件中的多项产品可加速车规级SoC级芯片的设计和资格认证:

专门针对ISO26262随机硬件故障进行开发和评估的ASIL B和D级就绪的IP;同时兼容ASIL D随机硬件故障和ASIL D系统故障的ARC处理器;ISO 9001认证的质量管理体系,根据AEC-Q100而设计和测试的IP,SoC级安全管理器;面向汽车0、1和2级温度的IP;以及基于22FDX和FinFET工艺的IP。

图片来源:新思科技

如何在软件智能化程度及部署复杂度不断拔高的同时保障产品可靠性?针对第一个问题,新思科技的答案是:提供通过了汽车工艺能力指数、百万分之缺陷率/PPM验证的IP方案,助力芯片通过严格的车规级安全标准审核。

虚拟原型技术:将软件先行落到实处

如何在代码数成倍增长、软件及部署复杂度不断拔高的同时加快供应速度?武钰对一套虚拟原型交样的方案进行了简要介绍:

将SoC级芯片方案虚拟化,在尚未流片前,让客户在PC端拿到芯片的数字化原型,最多提前18个月对软件进行部署和测试,在芯片制成后可以直接用开发成型的软件进行移植,由此加快软件研发的整体速度,进而缩短开发周期。

武钰介绍,这套方案已经在欧美实现多年,具有成熟的技术基础,并与诸多Tier 1, OEM厂商进行深层次的合作,这大幅扩展了新思科技的虚拟MCU/SoC模型库,这是新思科技提供SoC级虚拟原型和工具,支持多种模型和操作系统虚拟化的底气。

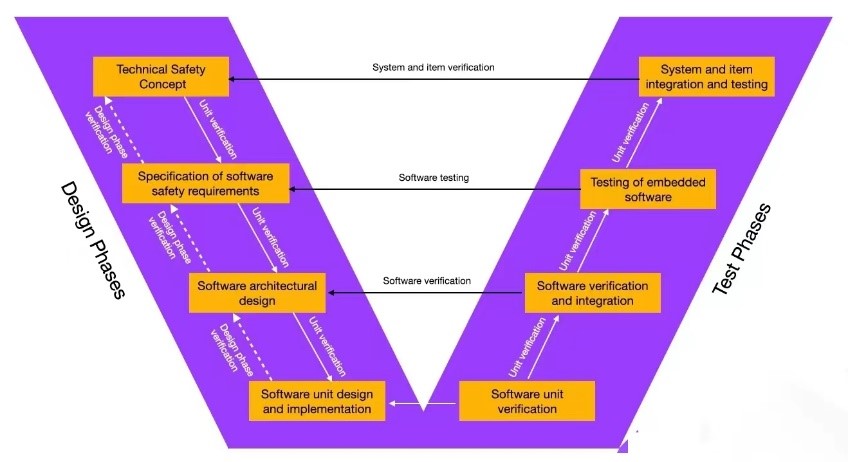

在传统汽车电子的V型开发流程中:从需求编译、单元测试(MISRA规则测试;Polyspace测试;功能测试;边界测试)、软件集成测试、硬件在环测试、最终进入实车测试。每一次改动都可能导致全局重来,可谓牵一发而动全身。

V型开发图

相比而言,虚拟原型验证可以为SoC级芯片的软件开发带来五处重要改进:

第一,将软件先行落到实处:在芯片制成12~18个月前开始软件开发。第二,大幅提高调试和分析效率。第三,易于将软件虚拟原型与主机服务器群进行配置并回归测试。第四,通过虚拟原型的软件易于量产分发,便于开发组内部和整条供应链实现协作,允许在芯片回片前共享设计。第五,虚拟原型提供了灵活、可扩展和可获得的手段,可以更早地进行证明设计。

总体而言,虚拟原型技术将极大提高生产效率,帮助开发者消除片上系统(SoC)设计过程中的不确定性。

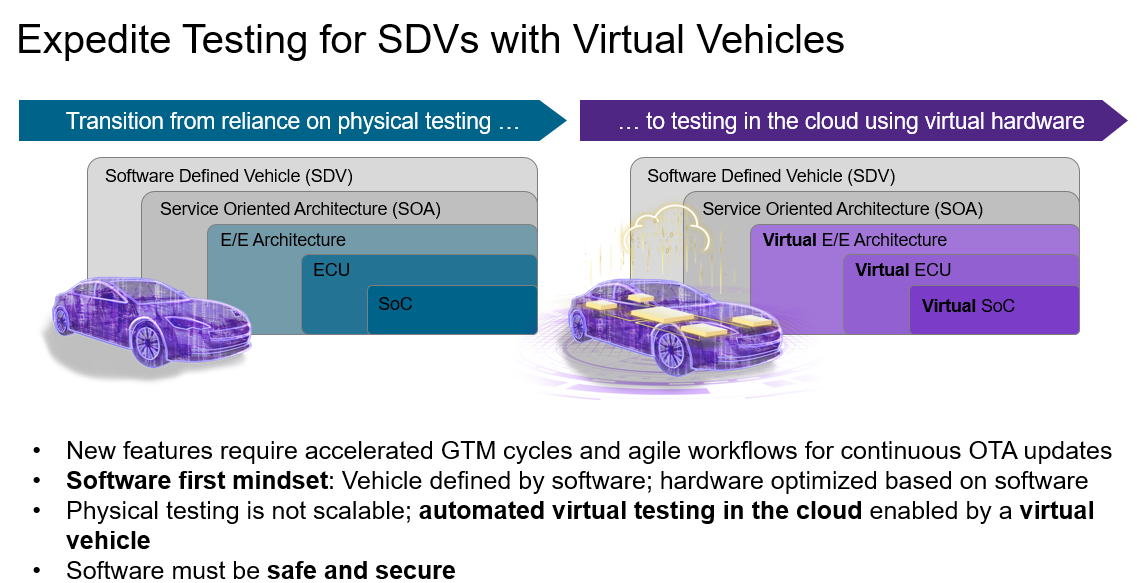

除了虚拟SoC,新思科技进一步还推出了更接近应用级的虚拟ECU方案:将ECU的应用层和通讯架构在虚拟原型中实现,顺应软件定义汽车的潮流,使汽车ECU开发升级为“由软及硬、软件主导”。武钰补充,这套工具目前已经支持云端级联架构,用户可在云端进行仿真测试。

图片来源:新思科技

目前,新思科技已经实现涵盖整车的全链条开发,有能力提供从芯片、软件到系统的车规级解决方案。行业趋势而言,从物理测试过渡到虚拟测试,从软件配合硬件走向软件先行、汽车行业从硬件部署走向软件定义的关键环节。

安全为重,SLM覆盖芯片的全生命周期监管

根据整车制造的时间线,纵览新思科技的产品覆盖面:芯片设计阶段,新思科技提供车规级IP与EDA全流程芯片设计解决方案;芯片开发阶段,新思科技的虚拟原型技术可以帮助客户实现软件先行,缩短研发周期;在软件及部署复杂度提升的大背景下,新思科技提供代码监测工具,帮助测试代码质量与排查安全漏洞。

随芯片迭代速率提升,针对个体而言,需要尽可能收集单个芯片全生命周期的有用数据;针对不同代际的芯片,则需要对数据进行分析对比,以获得改善下一代芯片和系统运行的可靠建议。

图片来源:新思科技

芯片如何做到“三省吾身”?新思科技的芯片生命周期管理平台 (SLM) 为这一痛点提供了解决方案,通过对芯片设计、制造、测试、最终用户系统部署的全过程进行追踪,对获取信息进行监控、分析和优化。

这些信息来源于工艺/电压/温度 (PVT) 传感器、可测性设计 (DFT) 和内置自测试 (BIST) 资源、结构和功能监控器、嵌入式片上分析组件。

通过这些嵌入式监控器和传感器,新思科技的SLM解决方案实现了芯片全生命周期、全使用场景覆盖,通过一系列数据关联性和根本原因分析,能够加速芯片的“良率学习”流程,从而优化最终产品良率,从而助推车规级芯片的实现。

从第一辆通用电动汽车的诞生,到智能电动时代来临,让人类不断点亮科技未来的不是零和博弈,而是生态网络中的平衡与共赢。在武钰看来,新思科技持续伴随国产芯片的成长,助力国产芯片上车,最终带来的将是产业生态的双赢共生。

(以上内容根据新思科技汽车业务拓展总监武钰于2022年8月4日由盖世汽车、AUTOSAR组织联合主办的2022第三届软件定义汽车论坛暨AUTOSAR中国日发表的《从芯片、软件到车载系统融合》主题演讲进行理解和整理。)

*版权声明:本文为盖世汽车原创文章,如欲转载请遵守 转载说明 相关规定。违反转载说明者,盖世汽车将依法追究其法律责任!

本文地址:https://auto.gasgoo.com/news/202208/22I70311572C103.shtml

好文章,需要你的鼓励

联系邮箱:info@gasgoo.com

求职应聘:021-39197800-8035

简历投递:zhaopin@gasgoo.com

客服微信:gasgoo12 (豆豆)

新闻热线:021-39586122

商务合作:021-39586681

市场合作:021-39197800-8032

研究院项目咨询:021-39197921